Tại sao Flash NAND và Controller quyết định hiệu năng của ổ cúng SSD

Như chúng ta đã biết, ổ cứng SSD không lưu dữ liệu trên các phiến đĩa và hoàn toàn không sử dụng đầu đọc. Thay vào đó, dữ liệu sẽ được lưu trên các chip nhớ kiến trúc NAND hay còn được biết đến dưới tên gọi flash NAND. Cấu tạo của flash NAND bao gồm nhiều bóng bán dẫn (transitor) đặc biệt có tên gọi floating gate transistor, được thiết kế để có thể giữ nguyên trạng thái cả khi không cấp nguồn. Đây cũng là điểm khác biệt với chip flash dùng trong bộ nhớ DRAM, vốn cần phải làm tươi nhiều lần mỗi giây và không lưu dữ liệu khi mất nguồn.

Các công nghệ flash NAND

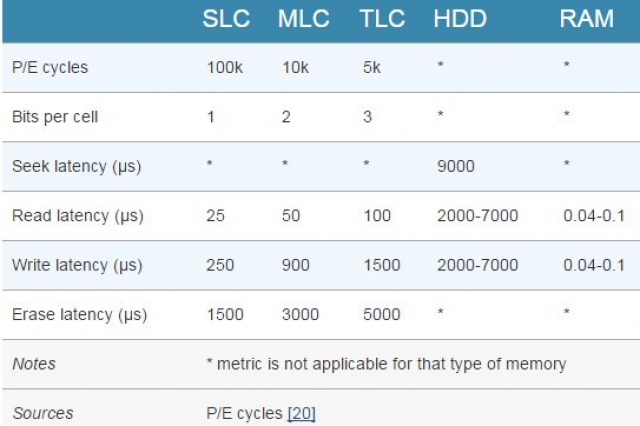

Có ba công nghệ flash NAND hiện đang sử dụng phổ biến trong SSD là SLC (single-level cell), MLC (multi-level cell) và TLC (triple-level cell). Sự khác nhau giữa các công nghệ này là mật độ bit dữ liệu chứa trong chip nhớ, độ trễ và độ bền dựa theo chu kỳ ghi xóa (P/E cycle). Và điều này ảnh hưởng trực tiếp đến hiệu năng tổng thể của SSD.

Theo bảng thông số kỹ thuật bên dưới cho thấy NAND SLC chỉ chứa 1 bit dữ liệu (0 hoặc 1) nhưng có độ trễ thấp nhất và độ bền đạt đến 100.000 chu kỳ ghi xóa. MLC chứa 2 bit dữ liệu và chu kỳ ghi xóa vào khoảng 10.000 lần. Trong khi đó, NAND TLC (triple level cell) chứa đến 3 bit dữ liệu nhưng vấn đề lớn nhất của công nghệ chip nhớ này là độ tin cậy thấp, chỉ 5.000 chu kỳ P/E và độ trễ cao hơn nhiều so với hai loại trên.

Về cơ bản, SSD sử dụng chip NAND TLC có tốc độ đọc lẫn ghi thấp hơn chip MLC, mặc dù mỗi cell của TLC chứa đến 3 bit dữ liệu. Ngược lại SSD dùng NAND SLC có hiệu năng và độ bền cao nhất đồng thời chi phí sản xuất cũng cũng đắt hơn nhiều, nên chỉ ứng dụng trong các hệ thống đòi hỏi độ bền và khả năng đáp ứng cùng lúc số lượt truy xuất dữ liệu lớn.

Về cấu trúc flash NAND được chia theo mô hình lưới, cơ bản là cell (ô nhớ), page (trang) và block (khối). Nhiều cell hợp thành một page, kích thước thường từ 2 - 16KB. Tương tự nhiều page sẽ tạo thành một block, gồm 128 đến 256 page với kích thước từ 256KB - 4MB. Trong xu hướng hiện nay, nhiều nhà sản xuất thường chọn cách mở rộng kích thước page và block để tăng tốc độ ghi của SSD.

Cơ chế hoạt động của flash NAND

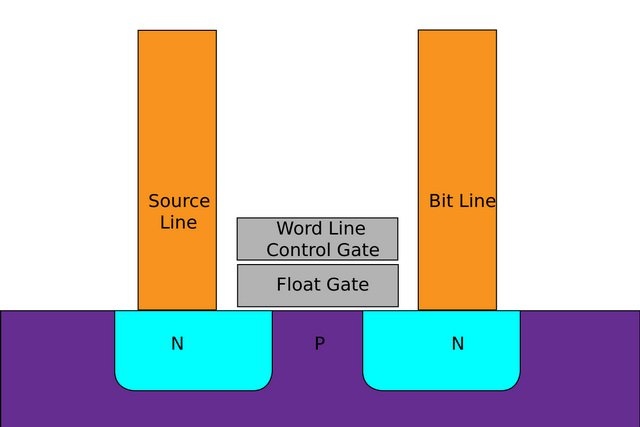

Hình minh họa trên cho thấy trong cấu tạo floating gate transistor có một cổng động (floating gate) nằm giữa cổng điều khiển (control gate) và đế silicon bên dưới. Đây cũng là nơi lưu một trong hai trạng thái là lập trình hoặc xóa để biểu thị một hai giá trị cơ bản là 0 hoặc 1 trong hệ nhị phân. Phủ quanh floating gate là một lớp mỏng chất liệu cách điện như dioxide silicon.

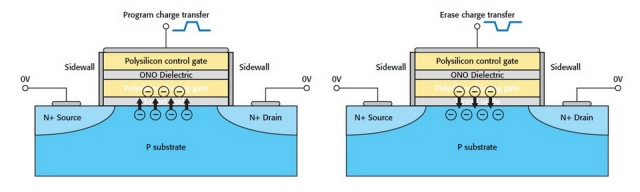

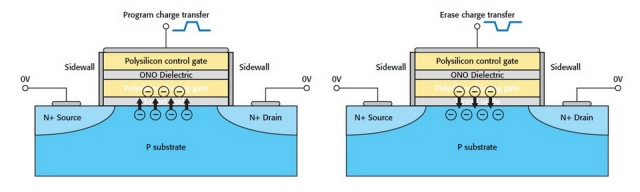

Ở trạng thái bình thường, giữa cực nguồn (source line) và cực dẫn (bit line) không xuất hiện dòng điện. Khi đặt điện áp dương vào cổng điều khiển thì giữa cực dẫn và cực nguồn sẽ hình thành dòng điện và đẩy electron từ đế silicon bên dưới qua lớp cách điện đi vào cổng động. Nhờ vậy trạng thái của cổng động có thể được xác định dựa trên sự thay đổi điện áp ngưỡng.

Với NAND SLC chỉ có hai mức trạng thái là lập trình hoặc xóa trong khi MLC có đến bốn mức và TLC là tám mức trạng thái điện áp ngưỡng. Về mặt lý thuyết, để một cell biểu diễn được được n bit nhị phân thì nó phải được thiết kế đạt 2n trạng thái khác nhau. Ứng với mỗi trạng thái, floating gate sẽ có một giá trị điện áp ngưỡng.

Sở dĩ NAND TLC có tốc độ chậm hơn MLC và SLC là do nó lưu trữ nhiều bit dữ liệu hơn. Đối với SLC thì chip điều khiển (controller) chỉ quan tâm đến hai mức là 0 hoặc 1 (tương ứng với lập trình hoặc xóa). NAND MLC thì mỗi cell chứa nhiều hơn, có 4 giá trị là 00, 01, 10 hoặc 11 trong khi NAND TLC lại chứa đến 8 giá trị. Việc đọc dữ liệu trong mỗi ô nhớ sẽ do bộ điều khiển quản lý thông qua mức điện áp ngưỡng.

Với NAND MLC và TLC, có ba yếu tố cần đảm bảo là:

- Electron nạp đúng vị trí. Quá trình lập trình ô nhớ đòi hỏi sự chính xác cao nên cần kiểm soát tốt từ cấp vật lý, nhất là yếu tố thời gian và mức điện áp nạp.

- Sự chính xác. Quá trình đọc dữ liệu trong công nghệ MLC và TLC thực chất là quá trình chuyển đổi giá trị từ dạng tương tự (analog) sang dạng số (digital) nên phép đọc giá trị điện áp ô nhớ cần sự chính xác cao. Nếu không, dữ liệu có thể sai lệch và gây lỗi.

- Tính ổn định trạng thái nạp. Đảm bảo tỷ lệ thất thoát trong cổng động không vượt quá 1 electron/ngày. Điều này cho thấy SSD vẫn có nguy cơ mất dữ liệu nếu bạn không sử dụng chúng trong một thời gian dài, đặc biệt là rủi ro này càng tăng trong môi trường nhiệt độ cao.

Tốc độ đọc, ghi và xóa

Một trong những hạn chế của SSD là tốc độ đọc và ghi trên cell trống rất nhanh nhưng lại giảm đáng kể trong lần ghi dữ liệu kế tiếp. Nguyên nhân nằm ở cơ chế hoạt động của SSD và cấu trúc flash NAND. Khác với ổ cứng truyền thống, SSD đọc và ghi dữ liệu theo từng page nhưng chỉ có thể xóa dữ liệu theo từng block. Trong khi đó, vấn đề của flash NAND là không cho phép ghi đè dữ liệu trực tiếp lên cell cũ mà phải qua bước xóa dữ liệu trước tiên.

Khi bạn xóa dữ liệu, chip điều khiển chỉ đơn giản đánh dấu các page đó chứ không thực sự xóa chúng cho đến khi đã cần sử dụng lại. Điều này cũng giải thích tại sao SSD càng sử dụng lâu, hiệu năng càng giảm. Trong một block bộ nhớ có thể tồn tại các page đang chứa dữ liệu lẫn một số page ở trạng thái chờ xóa. Để dọn dẹp, chip điều khiển sẽ chép dữ liệu sang một block mới và xóa toàn bộ block cũ, sẵn sàng cho một chu kỳ sử dụng mới. Quá trình này được gọi là garbage collection (tạm dịch thu gom rác).

Các tin liên quan

-

SSD là gì? SSD hoạt động như thế nào?

2.123 ngày trước -

Công nghệ chip nhớ trên ổ cứng SSD: SLC, MLC, TLC, QLC và PLC là gì?

2.376 ngày trước -

7 thuật ngữ cần biết khi mua ổ cứng SSD

2.889 ngày trước -

Tìm hiểu các thông số kỹ thuật trên ổ cứng SSD

2.895 ngày trước -

Cài game vào ổ cứng SSD, có phải sẽ làm ổ cứng của chúng ta nhanh hỏng hơn?

2.896 ngày trước -

Nên lựa chọn SSD sử dụng giao tiếp SATA hay PCI Express?

2.901 ngày trước -

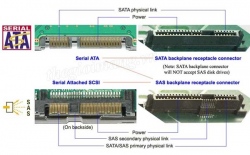

So sánh về chuẩn SATA và SAS cho ổ cứng máy chủ

2.903 ngày trước